| Dahili diferansiyel izolasyon dönüşüm |  |

| 16 bit çözünürlük | |

| Doğruluk: 2 açısal dakika | |

| Üç durumlu mandal çıkışı | |

| Yüksek sürekli izleme hızı | |

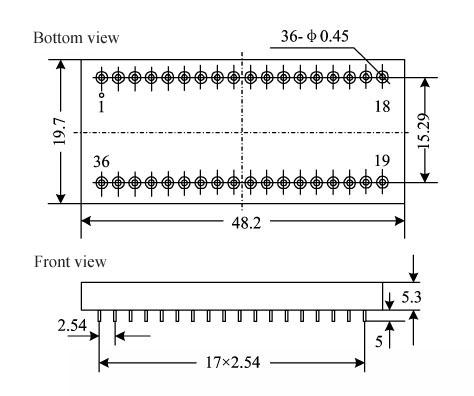

| 36 telli tuz sis dayanıklı metal sızdırmaz DDIP paket | |

| Pin-To-Pin DDC şirketinin Model SDC14560 ile uyumlu |

| üzerinde tasarlanmış sürekli izleme için entegre dönüştürme cihazı | model II servo prensibi. Bu seri ürünler tasarlanmış ve |

| MCM işlemi ile üretilen çekirdek elemanlar özel çip benimser | |

| Enstitümüz tarafından bağımsız olarak geliştirilmiştir. Pim düzeni | |

| Amerikan DDC şirketinin SDC14560 serisi ürünleri ile uyumlu, 16-bit | |

| paralel doğal ikili kod veri mandalı çıkışı, tamamen 36 satırlı DIP | |

| mühürlü metal paket, yüksek hassasiyet, küçük avantajlara sahiptir | |

| hacim, düşük güç tüketimi, hafiflik ve yüksek güvenilirlik vb. | gibi önemli stratejik ve taktik silahlarda yaygın olarak kullanılabilir. |

| uçak, donanma gemisi, top, füze, radar, tank vb. | |

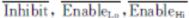

| 4. Elektrik performansı (Tablo 1, Tablo 2) | |

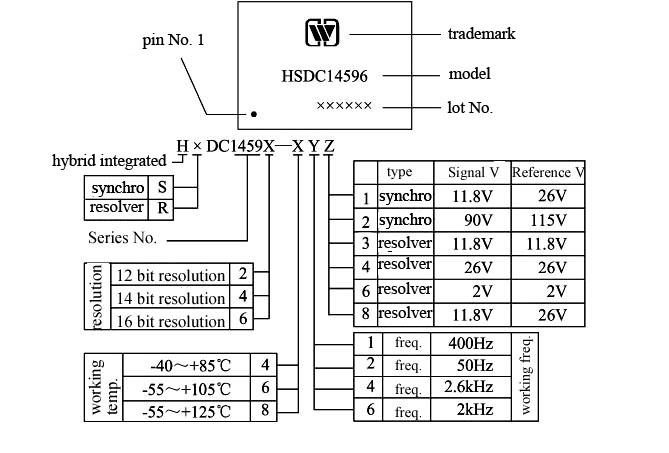

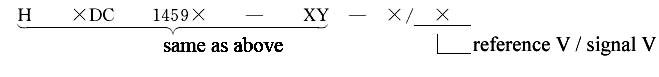

| Senkro - Dijital Dönüştürücüler veya Çözümleyici - Dijital Dönüştürücüler (HSDC/HRDC1459 Serisi) | |

| Tablo 1 Nominal koşullar ve önerilen çalışma koşulları | |

| Mutlak maks. anma değeri |

| Sinyal voltajı V1: nominal değer ±%20 | Referans voltajı VRef: nominal değer ±%20 | Çalışma frekansı f: nominal değer ±%20 | |

| Depolama sıcaklığı Tstg: -65~150℃ | Önerilen çalışma koşulları | ||

| Mantıksal besleme voltajı VL: 5±0,5V | Besleme gerilimi Vs: 15± 0,75V | ||

| Sinyal voltajı V1: nominal değer ±%10 | Referans voltajı VRef: nominal değer ±%20 | Çalışma frekansı f: nominal değer ±%20 | — |

| Çalışma sıcaklığı aralığı (TA): -55℃~125℃ | Not: *, kullanıcının ihtiyacına göre özelleştirilebileceğini belirtir. | Tablo 2 Elektrik özellikleri | Parametre |

| Koşullar | — | HSDC14569 Serisi | (VSu003d15V, VLu003d+5V) |

| Askeri standart (Q/HW20725-2006) | — | 2V | Min. |

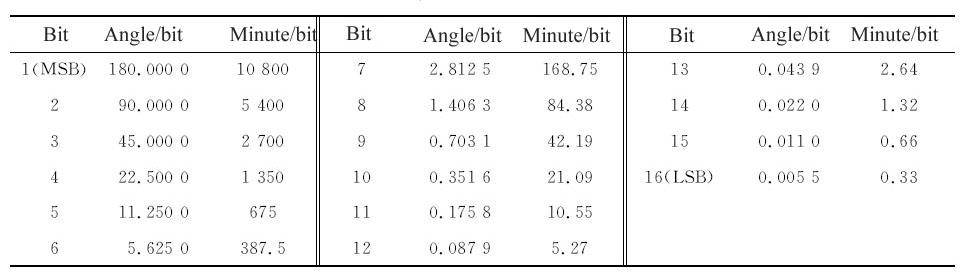

| Maks. | — | Çözünürlük | İkili sistem paralel dijital kodu |

| 16 bit | — | 2V | Kesinlik |

| ± %10 sinyal voltajı, referans gerilim ve çalışma frekansı dalgalanma aralığı | — | -2 açısal dakika | +2 açısal dakika |

| Referans sıklık aralığı | — | 50Hz | 2600Hz |

| Referans voltaj aralığı | — | 115V | Referans giriş empedansı |

4.4kΩ 4.4kΩ | — | 0 | 129,2 kΩ |

Sinyal voltajı aralığı Sinyal voltajı aralığı | — | 0 | 90V |

Sinyal giriş empedansı Sinyal giriş empedansı | — | 0 | 4.4kΩ |

| 102,2 kΩ | — | Sinyal/referans faz kayması | —70° |

| +70° | — | Giriş mantık düzeyi | Mantık "1" ≥3,3V |

| Mantık "0" ≤0,8V | — | giriş | 0.8V |

| giriş | — | 0.8V | |

| giriş | — | — | 0.8V |

| Çıkış mantık düzeyi | — | — | Mantık "1" ≥3,3V |

| Mantık "0" ≤0,8V | — | — | Dijital açı kodu çıktı |

| Mantık "1" ≥3,3V | — | — | Mantık "0" ≤0,8V |

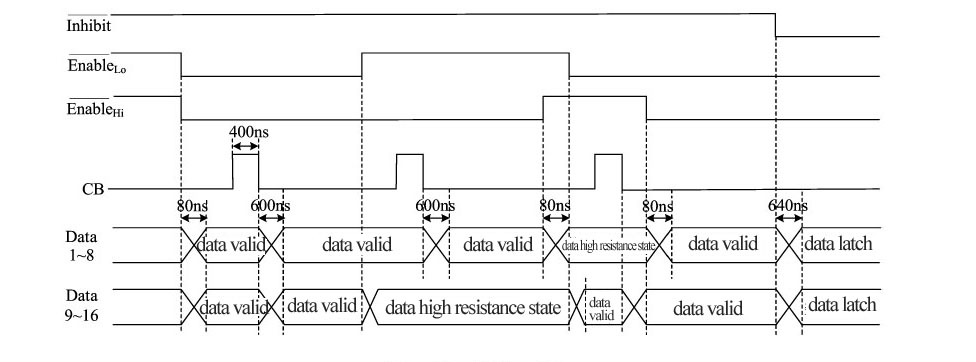

| Meşgul sinyali (CB) çıkışını dönüştürme | — | 200ns | 600ns |

| Hata algılama Bit çıktı | Mantık "0" hatayı gösterir | — | Yükleme kapasitesi |

| 3TTL | İzleme hızı | ||

| 2.5rps | Hızlanma sabiti | ||

| +10V Akım VSu003d+15V 10mA |  VS u003d—15V |

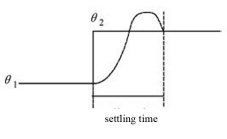

hız. Çıkış dijital açısının salınım süreci şu şekilde gösterilmektedir:

hız. Çıkış dijital açısının salınım süreci şu şekilde gösterilmektedir: 6. Çalışma prensibi (Şekil 3)

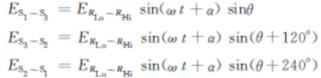

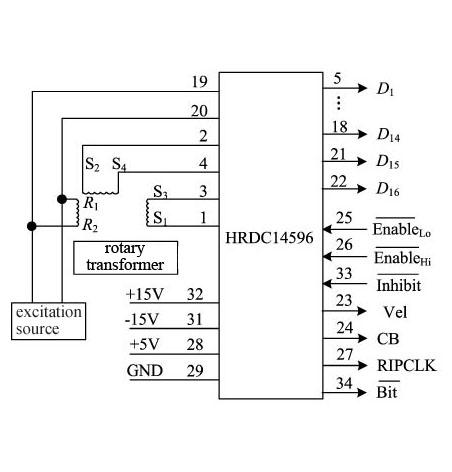

6. Çalışma prensibi (Şekil 3)| Senkro - Dijital Dönüştürücüler veya Çözümleyici - Dijital Dönüştürücüler (HSDC/HRDC1459 Serisi) Senkronun (veya çözücünün) giriş sinyali, dahili diferansiyel izolasyon yoluyla ortogonal sinyale dönüştürülür: | |

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofBurada, θ analog giriş açısıdır. Şekil 2 Adım yanıtının eğrisi | Bu iki sinyal ve dahili ters çevrilebilir sayacın dijital açısı φof Sinüs ve Kosinüs fonksiyonlarının çarpanında çarpılır ve tedavi edilen hata: |

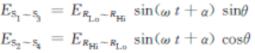

| amplifikasyon, faz ayrımı ve entegrasyon filtrasyonu, eğer | θ-φ≠0, voltaj kontrollü osilatör darbeleri çıkaracak ve | θ-φ doğruluğu içinde sıfır olana kadar tersinir sayaç sayıları | dönüştürücü, bu işlem sırasında, dönüşüm değişimini izler. | giriş açısı her zaman. | Okuma yöntemi: |

| 1 | S1 | Veri aktarımı için aşağıdaki iki yöntem mevcuttur: | 25 |  | (1) Engelleme yöntemi: |

| 2 | S2 | 640ns sonra | 26 |  | mantık düşük, çıkış verileri geçerlidir ve dönüştürücü, veri aktarımını gerçekleştirir |

| 3 | S3 | ve | 27 | . Engelleme serbest bırakıldıktan sonra, sistem veri güncelleme için otomatik olarak meşgul darbesine eşit genişlikte bir darbe oluşturur. | (2) Göğüs modu: |

| 4 | S4 | Meşgul nabzının yükselen kenarında, üç durumlu tersinir sayaç önemlidir; Meşgul darbesinin azalan kenarında, dahili olarak, üç durumlu mandalın verilerini güncellemek için Meşgul darbesine eşit bir genişliğe sahip bir mandal darbesi üretir, 600 veri showins'in diğer kelime transferinden sonraki zaman dizisi Meşgul mantığı düşük, veri kararlı aktarımı geçerlidir. Eşzamansız okuma modunda, Meşgul çıktı CMOS düzeyinde darbe tur. Yüksek ve düşük seviyesinin genişliği, seçilen cihazın çalışma frekansına ve dönüş hızına bağlıdır. | 28 | VL | Şekil.4 Veri aktarımının zaman sırası |

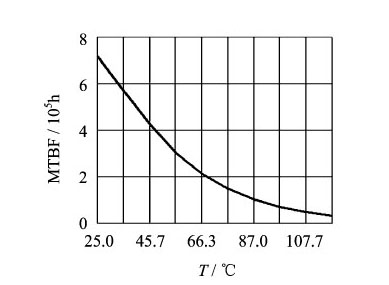

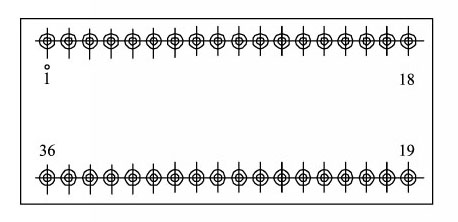

| 7. MTBF eğrisi (Şekil 5) | Senkro - Dijital Dönüştürücüler veya Çözümleyici - Dijital Dönüştürücüler (HSDC/HRDC1459 Serisi) | Şekil 5 MTBF-sıcaklık eğrisi | 29 | 8.Pin ataması (Şek.6, Tablo 3) | Senkro - Dijital Dönüştürücüler veya Çözümleyici - Dijital Dönüştürücüler (HSDC/HRDC1459 Serisi) |

| 19 | Şekil.6 Pin tanımı (Alttan görünüm) | (Not: GJB/Z299B-98'e göre, öngörülen iyi zemin durumu) | 30 | NC | Tablo 3 Pin tanımı |

| 20 | RL | Toplu iğne | 31 | sembol | Anlam |

| 21 | Toplu iğne | sembol | 32 | VS | Anlam |

| 22 | Çözümleyici girişi S1 (veya senkro girişi S1) | Daha düşük 8 bitlerin Dijital Etkin kontrolü | 33 | Çözümleyici girişi S2 (veya senkro giriş S2) | Daha yüksek 8 bitin Dijital Etkin kontrolü |

| 23 | Çözümleyici girişi S3 (veya senkro girişi S3) | RIPCLK | 34 | Sıfır bit sinyal çıkışı | Çözümleyici girişi S4 (bağlı olmadan bırakın) |

| 24 | CB | +5V güç kaynağı | 5月18日 | NC | D1-D14 |

| Dijital çıkış 1(MSB)-14 | GND |

| Zemin | RHi |

| Yüksek son başvuru sinyal girişi | Bağlantı yok |

| RL | Düşük referans sonu sinyali girişi |

-VS

-VS -15V Güç kaynağı

-15V Güç kaynağı

D15 Dijital çıkış 15

Dijital çıkış 15 ).

).

+15V Güç kaynağı

D16

Dijital çıkış 16 (LSB)

engelle

Statik sinyal girişi

kadife

S1, S2, S3, S4

S1, S2, S3, S4

Düşük referans sonu sinyali girişiofDaha düşük | 8 bit haneli etkin sinyal girişi, bu pin lojik giriş pinidir.ofveri geçiş kontrolü, işlevi üç durumlu kontrolü gerçekleştirmektir. |

|  |

| harici olarak dönüştürücünün alt 8 bitlik çıkış verilerinde. Düşük seviye | geçerli, dönüştürücünün alt 8 bitlik çıkış verileri verileri kaplar |

direnç durumu ve cihaz veri yolunu işgal etmez. Olanak vermekve serbest bırakma gecikme süresi 600ns'dir (maks). | daha yüksek | 8 bit haneli etkin sinyal girişi, bu pin lojik giriş pinidir. | veri geçiş kontrolü, işlevi üç durumlu kontrolü gerçekleştirmektir. | harici olarak dönüştürücünün daha yüksek 8 bitlik çıkış verilerinde. Düşük seviye | geçerlidir, dönüştürücünün daha yüksek 8 bitlik çıkış verisiveri yolu; Yüksek seviyede, daha yüksek 8 bitlik çıkış verilerinin pini yüksek | direnç durumu ve cihaz veri yolunu işgal etmez. Olanak vermek | ve serbest bırakma gecikme süresi 600ns'dir (maks). | Statik engelle |

sinyal girişi, bu pin kontrol mantığının giriş pinidir, işlevi | isteğe bağlı gerçekleştirmek için verileri harici olarak dönüştürücüye çıkarmaktır | Nikilitleme veya baypas kontrolü. Yüksek düzeyde, çıktı verileri | dönüştürücü doğrudan mandallama olmadan çıkış yapar; düşük seviyede, çıkış | dönüştürücünün verileri kilitlenir, veriler güncellenmez, ancakdahili döngü kesintiye uğramaz ve izleme tüm | zaman, Inhibit dahili olarak pull-up direncine sahiptir. 600ns (maks) gecikmeden sonra | Au Statik sinyalin azalan kenarı, veri kararlı hale gelir (ister | cihaz veri yolunu kaplar, yani veri ne zaman çıktı verirse bağlıdırdurumu hakkında | veCB “Meşgul” sinyal çıkışı, bu sinyalin ikili kod olup olmadığını gösterir. |

X

X