| Dahili diferansiyel izolasyon dönüşümü |  |

| Çözünürlük: 16 bit | |

| Üç durumlu mandal çıkışı | |

| Veri aktarımı sırasında kesintisiz izleme | |

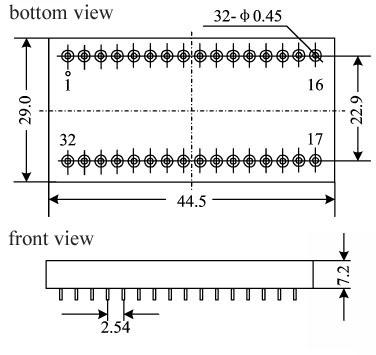

| 32 telli metal paket |

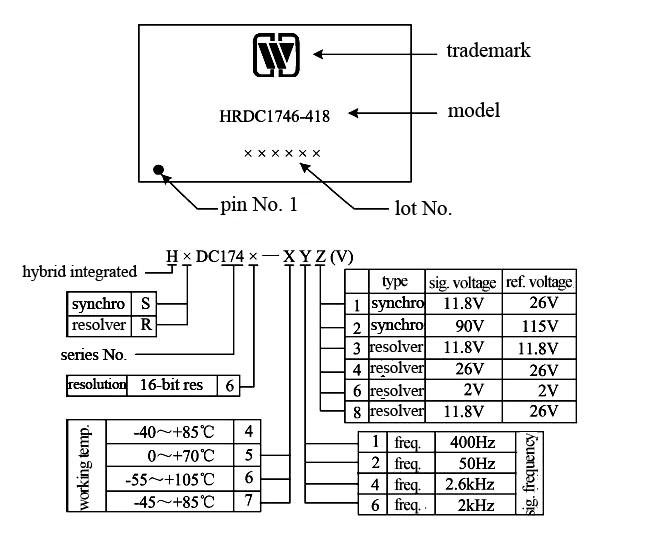

HSDC/HRDC1746 serisi senkro/çözücüden dijitale dönüştürücü tasarlanmıştır | tip II servo izleme prensibi prensibi üzerine ve benimser | |||||

diferansiyel izolasyon girişi, veri çıkışı üç durumlu mandalı benimser | modunda, analog sinyal/dijital sinyal dönüşümü için uygundur | üç kablolu senkro ve dört kablolu çözücü. Hızlı dönüşüm hızı ile | ve istikrarlı ve güvenilir performans, bu cihaz yaygın olarak uygulanabilir açı ölçümü ve otomatik kontrol sisteminde. | Bu ürün, kalın film hibrit entegrasyon işlemiyle yapılmıştır ve | ||

32 telli DIP tamamen kapalı metal paket. Hem tasarım hem | ||||||

ürünün imalatı GJB2438A-2002 gerekliliklerini karşılar | "Hibrit entegre devreler için genel özellikler" ve özel | ürünün özellikleri. | ||||

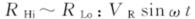

4. Elektrik performansı (Tablo 2, Tablo 3) | Senkro - Dijital Dönüştürücüler veya Çözümleyici - Dijital Dönüştürücüler (HSDC/HRDC1746 Serisi) | Tablo 2 Nominal koşullar ve önerilen çalışma koşulları | Tablo 3 Elektrik özellikleri | Mutlak maks. anma değeri | ||

Besleme gerilimi Vs: ± 17.25VDC | Parametre | -3 | 3 | |||

HSDC/HRDC | 1746 Serisi | 16 | ||||

notlar | Mantıksal besleme gerilimi VL: +7V | 50 | Depolama sıcaklığı aralığı: -55℃~150℃ | |||

Min. | Maks. | 2 | 90 | |||

Önerilen çalışma koşulları | Besleme gerilimi Vs: ±15± 5% | 2 | Doğruluk/açısal dakika | |||

| 2.6k |  |

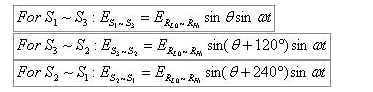

| Sinyal ve uyarım arasındaki faz kayması:<±%10 Sinyal voltajı (etkin değer)/V Çalışma sıcaklığı aralığı (TA): -40~+105℃  | |

| Referans voltajı (etkin değer)/V | 115 |

| |

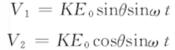

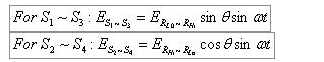

| bir hata fonksiyonu elde edilir: |

Hata amplifikasyonu, faz ayrımı ve bunun filtrasyonu yoluylaof hata fonksiyonu, sin(θ-φ) elde edilir, θ-φu003d0 olduğunda (doğruluk dahilinde | dönüştürücü), bu hata voltajı kontrollü hale getirecektir.ofikili dijital açıyı değiştirmek için osilatör çıkış düzeltme darbesi φ |

| |

| çıkış φ değerini şuna eşit yapmak için tersinir sayıcının | giriş θ dönüştürücünün doğruluğu dahilinde, sistem kararlı hale gelir |

| ve giriş açısının φ değişimini izleyebilir. Bu sayede ikili dijital | |

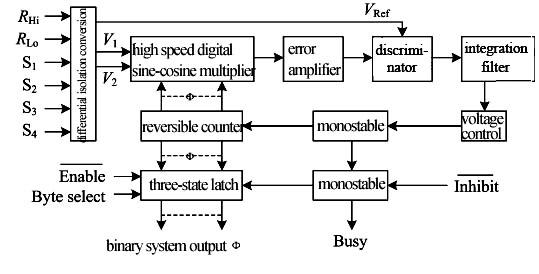

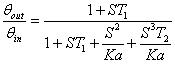

ters çevrilebilir sayaç (Şekil 2). | Şekil 2 Devre blok şeması | (1) Dinamik özellikler | Dönüştürücünün transfer fonksiyonu Şekil 3'te gösterilmektedir: | Açık döngü kazancı: | Kapalı döngü işlevi: |

1 | NC | Bu modelin modülü için Kau003d48000/S2, T1u003d7.1ms, T2u003d1.25ms | 17 | NC | Şekil 3 Dönüştürücünün işlev aktarımı |

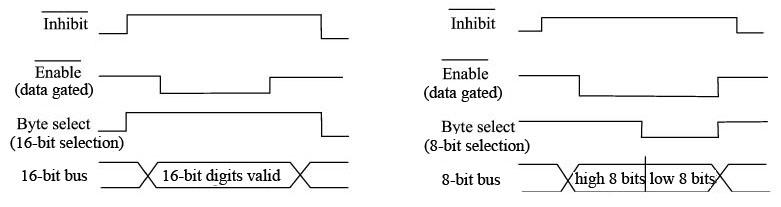

2 | D9 | (2)Veri aktarımı ve zaman sırası yöntemleri | 18 | Çip seçme kontrolü Etkinleştir | Bu pin kontrol mantığının giriş pinidir, işlevi çıkış yapmaktır. |

3 | Üç durumlu kontrolü gerçekleştirmek için dönüştürücüye veri. Düşük seviye | geçerliyse, dönüştürücünün çıkış verileri veri yolunu işgal eder. olduğu zaman | 19 | yüksek seviye, dönüştürücünün veri çıkış pimi üç durumda, | cihaz veri yolunu işgal etmez. |

4 | Bayt seçimi | Bu pin kontrol giriş pinidir, işlevi harici olarak çalıştırmaktır. | 20 | transferde dönüştürücünün çıkış verileri üzerinde seçim kontrolü | 8 bit veri yolu veya 16 bit veri yolu modu. 16 bit veri yolu aktarımı olduğunda |

5 | modu gereklidir, bu mantık pinini yüksek tutun, veriler | veriyoluna aktarıldığında, yüksek bayt çıkışı D1 ila D8 pinindedir (D1 | 21 | yüksek bit) ve düşük bayt D9 ila D16 arasındadır. 8 bit veri yolu aktarımı olduğunda | moduna ihtiyaç duyulursa, veriler D1 ila D8 pininde elde edilir (yüksekten düzenlenir) |

6 | düşük) ve yüksek 8 bit ve düşük 8 bit iki kez elde edilir | diziler, başka bir deyişle, Bayt seçimi mantık yüksek olduğunda, yüksek 8 bit | 22 | çıkıştır ve mantık düşük olduğunda, düşük 8 bit çıkış verilir. | Veri kilitleme kontrolü (Sinyali engelle) Engelle |

7 | Bu pin kontrol mantığının giriş pinidir, işlevi çıkış yapmaktır. | isteğe bağlı kilitleme veya baypas gerçekleştirmek için dönüştürücüye harici olarak veri | 23 | kontrol. Yüksek seviyede, dönüştürücünün çıkış verileri doğrudan | mandallama olmadan çıktı, verilerin zaman sırası diyagramına bakın |

8 | Aktar. Düşük seviyede, dönüştürücünün çıkış verileri kilitlenir, | dahili döngü kesintiye uğramaz ve izleme tüm süreç boyunca çalışmaya devam eder. | 24 | D1 | ancak sayaç veri çıkışı yapmaz. Aktarmak gerektiğinde |

9 | dönüştürücü önce verileri yüksekten düşüğe kilitlemek için Kontrol sinyalini engelle, mantığı 640ns için düşük tutar, ardından Etkinleştirme girişini düşük olarak ayarlayın (şu anda cihaz veri yolunu işgal eder) ve ardından | Bayt seçimi yoluyla veri alır, ardından tüm kontrol mantıklarını yüksek seviyeye getirin | 25 | D2 | aktarmaya hazırlanmak için verileri yenilemek ve kilitlemek için |

10 | sonraki veri, lütfen veri aktarımının zaman sırası diyagramlarına bakın Fig.4 | ve Şekil 5. | 26 | D3 | (3)Giriş sinyalinin zayıflama yöntemi (Şekil 4 ve Şekil 5) |

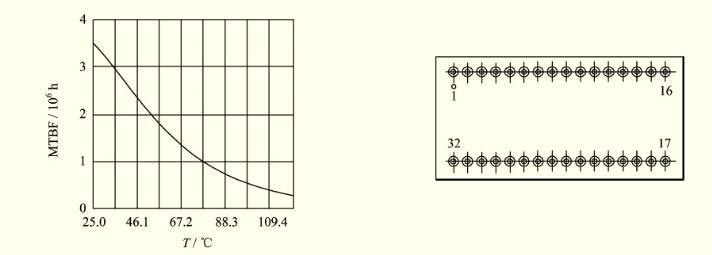

11 | Şekil 4 16 bit veri yolu aktarımının zaman dizisi | Şekil 5 8 bit veri yolu aktarımının zaman dizisi | 27 | D4 | 6. MTBF eğrisi (Şekil 6) |

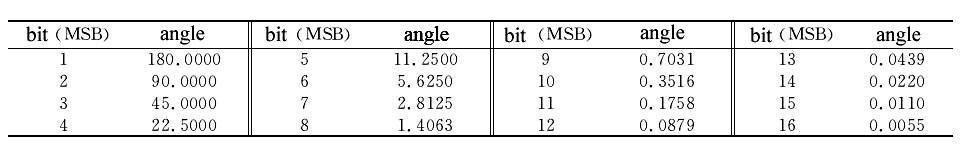

12 | Senkro - Dijital Dönüştürücüler veya Çözümleyici - Dijital Dönüştürücüler (HSDC/HRDC1746 Serisi) | 7. Pin tanımı (Şekil 7, Tablo 4) | 28 | D5 | Senkro - Dijital Dönüştürücüler veya Çözümleyici - Dijital Dönüştürücüler (HSDC/HRDC1746 Serisi) |

13 | S3 | Şekil.6 MTBF-sıcaklık eğrisi | 29 | D6 | Fig.7 Pin tanımı (Alttan görünüm) |

14 | S2 | (Not: GJB/Z299B-98 uyarınca, öngörülen iyi zemin koşulu) | 30 | D7 | Tablo 4 Lead terminallerinin işlevsel açıklaması |

15 | S1 | Toplu iğne | 31 | D7 | sembol |

16 | NC | Anlam | 32 | NC | Toplu iğne |

Zemin | D12 | 12thbit için dijital çıkış | -VS | -15V güç kaynağı | D13 | 13thbit için dijital çıkış | + VS | +15V güç kaynağı |

D14 | 14thbit için dijital çıkış | Ni | engelle | Ni | Veri kilitleme kontrolü | D15 | 15thbit için dijital çıkış |

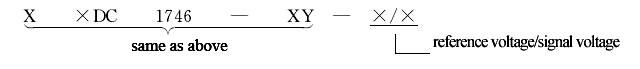

X

X